MICROCHIP PIC24 Flash Programming

Impormasyon ng Produkto

Flash Programming

Ang mga pamilya ng dsPIC33/PIC24 ng mga device ay may panloob na programmable Flash program memory para sa pagpapatupad ng user code. Mayroong hanggang tatlong paraan upang i-program ang memorya na ito:

- Pagpapatakbo ng Pagtuturo ng Table

- In-Circuit Serial Programming (ICSP)

- In-Application Programming (IAP)

Ang mga tagubilin sa talahanayan ay nagbibigay ng paraan ng paglilipat ng data sa pagitan ng Flash program memory space at ng data memory space ng dsPIC33/PIC24 device. Ang pagtuturo ng TBLRDL ay ginagamit upang basahin mula sa mga bits[15:0] ng espasyo ng memorya ng programa. Ang pagtuturo ng TBLWTL ay ginagamit upang magsulat sa mga bits[15:0] ng Flash program memory space. Maaaring ma-access ng TBLRDL at TBLWTL ang Flash program memory sa Word mode o Byte mode.

Bilang karagdagan sa Flash program memory address, ang pagtuturo ng talahanayan ay tumutukoy din sa isang W register (o isang W Register Pointer sa isang lokasyon ng memorya), iyon ang pinagmulan ng Flash program memory data na isusulat, o ang destinasyon para sa isang Flash program binasa ng memorya.

Inilalarawan ng seksyong ito ang pamamaraan para sa pagprograma ng Flash program memory. Ang mga pamilya ng dsPIC33/ PIC24 ng mga device ay may panloob na programmable Flash program memory para sa pagpapatupad ng user code. Mayroong hanggang tatlong paraan upang i-program ang memorya na ito:

- Run-Time Self-Programming (RTSP)

- In-Circuit Serial Programming™ (ICSP™)

- Pinahusay na In-Circuit Serial Programming (EICSP)

Ang RTSP ay ginagawa ng software ng application sa panahon ng pagpapatupad, habang ang ICSP at EICSP ay ginagawa mula sa isang panlabas na programmer gamit ang isang serial data connection sa device. Ang ICSP at EICSP ay nagbibigay-daan sa mas mabilis na oras ng programming kaysa sa RTSP. Ang mga diskarte sa RTSP ay inilarawan sa Seksyon 4.0 "Run-Time Self-Programming (RTSP)". Ang mga protocol ng ICSP at EICSP ay tinukoy sa mga dokumento ng Programming Specification para sa kani-kanilang mga device, na maaaring ma-download mula sa Microchip weblugar (http://www.microchip.com). Kapag nagprograma sa wikang C, maraming mga built-in na function ang magagamit na nagpapadali sa Flash programming. Tingnan ang “MPLAB® XC16 C Compiler User's Guide” (DS50002071) para sa mga detalye tungkol sa mga built-in na function.

Mga Tagubilin sa Paggamit ng Produkto

Upang i-program ang Flash program memory, sundin ang mga hakbang na ito:

- Sumangguni sa sheet ng data ng device upang tingnan kung sinusuportahan ng seksyong manual ng sangguniang pampamilya ang device na iyong ginagamit.

- I-download ang data sheet ng device at mga seksyon ng manual reference ng pamilya mula sa Microchip Worldwide Website sa: http://www.microchip.com.

- Pumili ng isa sa tatlong paraan upang i-program ang memorya (Table Instruction Operation, In-Circuit Serial Programming (ICSP), In-Application Programming (IAP)).

- Kung gumagamit ng Table Instruction Operation, gamitin ang TBLRDL instruction para magbasa mula sa bits[15:0] ng program memory space at ang TBLWTL instruction na magsulat sa bits[15:0] ng Flash program memory space.

- Siguraduhing tukuyin ang isang W register (o isang W Register Pointer sa isang lokasyon ng memorya) bilang ang pinagmulan ng Flash program memory data na isusulat, o ang destinasyon para sa isang Flash program memory read.

Para sa karagdagang impormasyon at mga detalye sa pagprograma ng Flash program memory, sumangguni sa dsPIC33/PIC24 Family Reference Manual.

TABLE INSTRUCTION OPERATION

Ang mga tagubilin sa talahanayan ay nagbibigay ng paraan ng paglilipat ng data sa pagitan ng Flash program memory space at ng data memory space ng dsPIC33/PIC24 device. Ang seksyong ito ay nagbibigay ng buod ng mga tagubilin sa talahanayan na ginamit sa pagprograma ng memorya ng programa ng Flash. Mayroong apat na pangunahing tagubilin sa talahanayan:

- TBLRDL: Mababa ang Binasang Talahanayan

- TBLRDH: Table Read High

- TBLWTL: Mababa ang Isulat sa Talahanayan

- TBLWTH: Mataas na Sumulat sa Talahanayan

Ang pagtuturo ng TBLRDL ay ginagamit upang basahin mula sa mga bits[15:0] ng espasyo ng memorya ng programa. Ang pagtuturo ng TBLWTL ay ginagamit upang magsulat sa mga bits[15:0] ng Flash program memory space. Maaaring ma-access ng TBLRDL at TBLWTL ang Flash program memory sa Word mode o Byte mode.

Ang mga tagubilin ng TBLRDH at TBLWTH ay ginagamit upang basahin o isulat sa mga bit[23:16] ng espasyo ng memorya ng programa. Maaaring ma-access ng TBLRDH at TBLWTH ang Flash program memory sa Word o Byte mode. Dahil ang Flash program memory ay 24 bits lang ang lapad, ang TBLRDH at TBLWTH na mga tagubilin ay maaaring tumugon sa isang itaas na byte ng Flash program memory na wala. Ang byte na ito ay tinatawag na "phantom byte". Anumang nabasa ng phantom byte ay magbabalik ng 0x00. Ang pagsulat sa phantom byte ay walang epekto. Ang 24-bit Flash program memory ay maaaring ituring bilang dalawang magkatabi na 16-bit na espasyo, na ang bawat espasyo ay nagbabahagi ng parehong hanay ng address. Samakatuwid, ang mga tagubilin ng TBLRDL at TBLWTL ay nag-a-access sa "mababang" memory space ng programa (PM[15:0]). Ang mga tagubilin ng TBLRDH at TBLWTH ay nag-a-access sa "high" memory space ng program (PM[31:16]). Anumang pagbabasa o pagsusulat sa PM[31:24] ay maa-access ang phantom (hindi naipatupad) na byte. Kapag ginamit ang alinman sa mga tagubilin sa talahanayan sa Byte mode, ang Least Significant bit (LSb) ng table address ay gagamitin bilang byte select bit. Tinutukoy ng LSb kung aling byte sa mataas o mababang espasyo ng memorya ng programa ang naa-access.

Ang Figure 2-1 ay naglalarawan kung paano tinutugunan ang memorya ng programa ng Flash gamit ang mga tagubilin sa talahanayan. Ang isang 24-bit na program memory address ay nabuo gamit ang mga bits[7:0] ng TBLPAG register at ang Effective Address (EA) mula sa isang W register na tinukoy sa pagtuturo ng talahanayan. Ang 24-bit Program Counter (PC) ay inilalarawan sa Figure 2-1 para sa sanggunian. Ang itaas na 23 bits ng EA ay ginagamit upang piliin ang lokasyon ng memorya ng programa ng Flash.

Para sa mga tagubilin sa talahanayan ng Byte mode, ang LSb ng W register EA ay ginagamit upang piliin kung aling byte ng 16-bit na Flash program memory word ang tinutugunan; Ang '1' ay pumipili ng mga bit[15:8] at ang '0' ay pumipili ng mga bit[7:0]. Ang LSb ng W register EA ay binabalewala para sa isang pagtuturo ng talahanayan sa Word mode. Bilang karagdagan sa Flash program memory address, ang pagtuturo ng talahanayan ay tumutukoy din sa isang W register (o isang W Register Pointer sa isang lokasyon ng memorya), iyon ang pinagmulan ng Flash program memory data na isusulat, o ang destinasyon para sa isang Flash program binasa ng memorya. Para sa pagpapatakbo ng pagsulat ng talahanayan sa Byte mode, ang mga bit[15:8] ng source na Working register ay binabalewala.

Paggamit ng Mga Tagubilin sa Pagbasa ng Talahanayan

Ang pagbabasa ng talahanayan ay nangangailangan ng dalawang hakbang:

- Ang Address Pointer ay naka-set up gamit ang TBLPAG register at isa sa mga W register.

- Maaaring basahin ang mga nilalaman ng memorya ng Flash program sa lokasyon ng address.

- BASAHIN ANG WORD MODE

Ang code na ipinapakita sa Halample 2-1 at HalampIpinapakita ng le 2-2 kung paano magbasa ng salita ng Flash program memory gamit ang mga tagubilin sa talahanayan sa Word mode.

- BASAHIN BYTE MODE

Ang code na ipinapakita sa HalampAng le 2-3 ay nagpapakita ng post-increment operator sa nabasa ng mababang byte, na nagiging sanhi ng address sa Working register na tumaas ng isa. Itinatakda nito ang EA[0] sa isang '1' para sa pag-access sa gitnang byte sa ikatlong pagtuturo ng pagsulat. Ang huling post-increment ay nagtatakda ng W0 pabalik sa isang pantay na address, na tumuturo sa susunod na lokasyon ng memorya ng programa ng Flash.

- TABLE WRITE LATCHES

Ang mga tagubilin sa pagsulat ng talahanayan ay hindi direktang sumulat sa memorya ng nonvolatile na programa. Sa halip, ang mga tagubilin sa pagsulat ng talahanayan ay naglo-load ng mga latch ng pagsulat na nag-iimbak ng data ng pagsusulat. Dapat na mai-load ang mga rehistro ng NVM Address ng unang address kung saan dapat isulat ang naka-latch na data. Kapag na-load na ang lahat ng write latches, magsisimula ang aktwal na operasyon ng memory programming sa pamamagitan ng pagsasagawa ng espesyal na pagkakasunod-sunod ng mga tagubilin. Sa panahon ng programming, inililipat ng hardware ang data sa mga write latches sa Flash memory. Palaging nagsisimula ang mga write latch sa address na 0xFA0000, at umaabot hanggang 0xFA0002 para sa word programming, o sa pamamagitan ng 0xFA00FE para sa mga device na mayroong row programming.

Tandaan: Ang bilang ng mga write latch ay nag-iiba ayon sa device. Sumangguni sa kabanata ng “Flash Program Memory” ng partikular na data sheet ng device para sa bilang ng mga available na write latches.

CONTROL REGISTERS

Ilang Special Function Registers (SFRs) ang ginagamit upang i-program ang Flash program memory erase at write operations: NVMCON, NVMKEY, at ang NVM Address registers, NVMADR at NVMADRU.

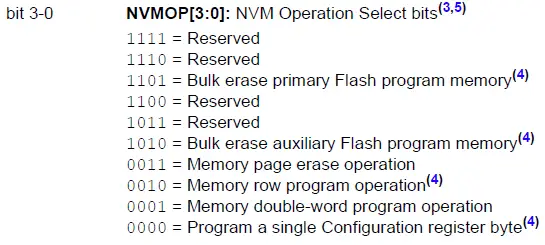

NVMCON Register

Ang NVMCON register ay ang pangunahing control register para sa Flash at program/erase operations. Pinipili ng register na ito kung isasagawa ang isang bura o pagpapatakbo ng program at maaaring simulan ang programa o ikot ng burahin. Ang rehistro ng NVMCON ay ipinapakita sa Register 3-1. Kino-configure ng mas mababang byte ng NVMCON ang uri ng operasyon ng NVM na isasagawa.

NVMKEY Register

Ang rehistro ng NVMKEY (tingnan ang Register 3-4) ay isang write-only na rehistro na ginagamit upang maiwasan ang mga aksidenteng pagsusulat ng NVMCON na maaaring masira ang Flash memory. Kapag na-unlock, ang pagsusulat sa NVMCON ay pinahihintulutan para sa isang ikot ng pagtuturo kung saan ang WR bit ay maaaring itakda upang mag-invoke ng bura o program routine. Dahil sa mga kinakailangan sa tiyempo, kinakailangan ang hindi pagpapagana ng mga pagkagambala.

Gawin ang mga sumusunod na hakbang upang magsimula ng pagbura o pagkakasunud-sunod ng programming:

- Huwag paganahin ang mga pagkagambala.

- Sumulat ng 0x55 sa NVMKEY.

- Isulat ang 0xAA sa NVMKEY.

- Simulan ang programming write cycle sa pamamagitan ng pagtatakda ng WR bit (NVMCON[15]).

- Magsagawa ng dalawang tagubilin sa NOP.

- Ibalik ang mga pagkagambala.

PAG-disable sa mga pagkagambala

Ang hindi pagpapagana ng mga pagkagambala ay kinakailangan para sa lahat ng mga pagpapatakbo ng Flash upang matiyak ang isang matagumpay na resulta. Kung ang isang interrupt ay nangyari sa panahon ng NVMKEY unlock sequence, maaari nitong harangan ang pagsulat sa WR bit. Ang pagkakasunud-sunod ng pag-unlock ng NVMKEY ay dapat na isagawa nang walang pagkaantala, gaya ng tinalakay sa Seksyon 3.2 “NVMKEY Register”.

Maaaring hindi paganahin ang mga interrupt sa isa sa dalawang pamamaraan, sa pamamagitan ng hindi pagpapagana sa Global Interrupt Enable (GIE bit), o sa pamamagitan ng paggamit ng DSI instruction. Hindi inirerekomenda ang pagtuturo ng DSI dahil hindi pinapagana nito ang mga interrupts ng Priority 6 o mas mababa; samakatuwid, ang paraan ng Global Interrupt Enable ay dapat gamitin.

Nagsusulat ang CPU sa GIE na tumagal ng dalawang ikot ng pagtuturo bago maapektuhan ang daloy ng code. Dalawang tagubilin sa NOP ang kailangan pagkatapos, o maaaring palitan ng anumang iba pang kapaki-pakinabang na tagubilin sa trabaho, tulad ng pag-load ng NVMKEY; naaangkop ito sa parehong nakatakda at malinaw na mga operasyon. Dapat gawin ang pag-iingat kapag muling pinapagana ang mga interrupt upang ang naka-target na routine ng NVM ay hindi payagan ang mga interrupts kapag ang isang dating tinatawag na function ay hindi pinagana ang mga ito para sa iba pang mga kadahilanan. Upang matugunan ito sa Assembly, maaaring gamitin ang stack push at pop para mapanatili ang estado ng GIE bit. Sa C, ang isang variable sa RAM ay maaaring gamitin upang mag-imbak ng INTCON2 bago i-clear ang GIE. Gamitin ang sumusunod na pagkakasunud-sunod upang huwag paganahin ang mga pagkagambala:

- Itulak ang INTCON2 sa stack.

- I-clear ang GIE bit.

- Dalawang NOP o sumusulat sa NVMKEY.

- Simulan ang programming cycle sa pamamagitan ng pagtatakda ng WR bit (NVMCON[15]).

- I-restore ang GIE state sa pamamagitan ng POP ng INTCON2.

Mga Rehistro ng NVM Address

Ang dalawang NVM Address na nagrerehistro, ang NVMADRU at NVMADR, kapag pinagsama, ay bumubuo ng 24-bit na EA ng napiling row o salita para sa mga pagpapatakbo ng programming. Ang NVMADRU register ay ginagamit upang hawakan ang itaas na walong bits ng EA, at ang NVMADR register ay ginagamit upang hawakan ang mas mababang 16 bits ng EA. Ang ilang device ay maaaring sumangguni sa mga parehong register na ito bilang NVMADRL at NVMADRH. Ang mga rehistro ng NVM Address ay dapat palaging tumuturo sa isang double instruction word boundary kapag nagsasagawa ng double instruction word programming operation, isang row boundary kapag nagsasagawa ng row programming operation o isang page boundary kapag nagsasagawa ng page erase operation.

Register 3-1: NVMCON: Flash Memory Control Register

Tandaan

- Ang bit na ito ay maaari lamang i-reset (ibig sabihin, i-clear) sa isang Power-on Reset (POR).

- Kapag lumalabas sa Idle mode, mayroong power-up delay (TVREG) bago gumana ang Flash program memory. Sumangguni sa kabanata ng "Mga Katangian ng Elektrisidad" ng partikular na sheet ng data ng device para sa higit pang impormasyon.

- Ang lahat ng iba pang kumbinasyon ng NVMOP[3:0] ay hindi naipatupad.

- Hindi available ang functionality na ito sa lahat ng device. Sumangguni sa kabanata ng “Flash Program Memory” sa partikular na data sheet ng device para sa mga available na operasyon.

- Ang pagpasok sa power-saving mode pagkatapos magsagawa ng PWRSAV instruction ay nakasalalay sa pagkumpleto ng lahat ng nakabinbing operasyon ng NVM.

- Available lang ang bit na ito sa mga device na sumusuporta sa RAM buffered row programming. Sumangguni sa data sheet na partikular sa device para sa availability.

Tandaan

- Ang bit na ito ay maaari lamang i-reset (ibig sabihin, i-clear) sa isang Power-on Reset (POR).

- Kapag lumalabas sa Idle mode, mayroong power-up delay (TVREG) bago gumana ang Flash program memory. Sumangguni sa kabanata ng "Mga Katangian ng Elektrisidad" ng partikular na sheet ng data ng device para sa higit pang impormasyon.

- Ang lahat ng iba pang kumbinasyon ng NVMOP[3:0] ay hindi naipatupad.

- Hindi available ang functionality na ito sa lahat ng device. Sumangguni sa kabanata ng “Flash Program Memory” sa partikular na data sheet ng device para sa mga available na operasyon.

- Ang pagpasok sa power-saving mode pagkatapos magsagawa ng PWRSAV instruction ay nakasalalay sa pagkumpleto ng lahat ng nakabinbing operasyon ng NVM.

- Available lang ang bit na ito sa mga device na sumusuporta sa RAM buffered row programming. Sumangguni sa data sheet na partikular sa device para sa availability.

Register 3-2: NVMADRU: Nonvolatile Memory Upper Address Register

Register 3-3: NVMADR: Nonvolatile Memory Address Register

Register 3-4: NVMKEY: Nonvolatile Memory Key Register

RUN-TIME SELF-PROGRAMMING (RTSP)

Pinapayagan ng RTSP ang application ng gumagamit na baguhin ang mga nilalaman ng memorya ng programa ng Flash. Naisasagawa ang RTSP gamit ang TBLRD (Table Read) at TBLWT (Table Write) na mga tagubilin, ang TBLPAG register, at ang NVM Control registers. Sa RTSP, maaaring burahin ng application ng user ang isang pahina ng Flash memory at programa ng alinman sa dalawang salita ng pagtuturo o hanggang 128 na salita ng pagtuturo sa ilang partikular na device.

Operasyon ng RTSP

The dsPIC33/PIC24 Flash program memory array is organized into erase pages that can contain up to 1024 instructions. The double-word programming option is available in all devices in the dsPIC33/PIC24 families. In addition, certain devices have row programming capability, which allows the programming of up to 128 instruction words at a time. Programming and erase operations always occur on an even double programming word, row or page boundaries. Refer to the “Flash Program Memory” chapter of the specific device data sheet for the availability and sizes of a programming row, and the page size for erasing. The Flash program memory implements holding buffers, called write latches, that can contain up to 128 instructions of programming data depending on the device. Prior to the actual programming operation, the write data must be loaded into the write latches. The basic sequence for RTSP is to set up the Table Pointer, TBLPAG register, and then perform a series of TBLWT instructions to load the write latches. Programming is performed by setting the control bits in the NVMCON register. The number of TBLWTL and TBLWTH instructions needed to load the write latches is equal to the number of program words to be written.

Tandaan: Inirerekomenda na ang rehistro ng TBLPAG ay i-save bago ang pagbabago at ibalik pagkatapos gamitin.

MAG-INGAT

Sa ilang device, ang Configuration bits ay iniimbak sa huling page ng program Flash user memory space sa isang seksyon na tinatawag na, “Flash Configuration Bytes”. Sa mga device na ito, ang pagsasagawa ng pagpapatakbo ng pagbubura ng pahina sa huling pahina ng memorya ng program ay binubura ang mga byte ng Flash Configuration, na nagbibigay-daan sa proteksyon ng code. Samakatuwid, ang mga gumagamit ay hindi dapat magsagawa ng mga pagpapatakbo ng pagbubura ng pahina sa huling pahina ng memorya ng programa. Hindi ito isang alalahanin kapag ang mga Configuration bit ay naka-store sa Configuration memory space sa isang seksyon na tinatawag na, “Device Configuration Registers”. Sumangguni sa Program Memory Map sa "Memory Organization" na kabanata ng partikular na data sheet ng device upang matukoy kung saan matatagpuan ang Configuration bits.

Mga Operasyon ng Flash Programming

A program or erase operation is necessary for programming or erasing the internal Flash program memory in RTSP mode. The program or erase operation is automatically timed by the device (refer to the specific device data sheet for timing information). Setting the WR bit (NVMCON[15]) starts the operation. The WR bit is automatically cleared when the operation is finished. The CPU stalls until the programming operation is finished. The CPU will not execute any instructions or respond to interrupts during this time. If any interrupts occur during the programming cycle, they will remain pending until the cycle completes. Some dsPIC33/PIC24 devices may provide auxiliary Flash program memory (refer to the “Memory Organization” chapter of the specific device data sheet for details), which allows instruction execution without CPU Stalls while user Flash program memory is being erased and/ or programmed. Conversely, auxiliary Flash program memory can be programmed without CPU Stalls, as long as code is executed from the user Flash program memory. The NVM interrupt can be used to indicate that the programming operation is complete.

Tandaan

- Kung ang isang POR o BOR na kaganapan ay nangyari habang ang isang RTSP erase o programming operation ay isinasagawa, ang RTSP operation ay agad na aabort. Dapat isagawa muli ng user ang pagpapatakbo ng RTSP pagkatapos lumabas ang device sa Reset.

- Kung ang isang EXTR, SWR, WDTO, TRAPR, CM o IOPUWR Reset na kaganapan ay nangyari habang ang isang RTSP erase o programming operation ay isinasagawa, ang device ay mare-reset lamang pagkatapos makumpleto ang RTSP operation.

RTSP PROGRAMMING ALGORITHM

Inilalarawan ng seksyong ito ang RTSP programming, na binubuo ng tatlong pangunahing proseso.

Paglikha ng RAM Image ng Data Page na Babaguhin

Gawin ang dalawang hakbang na ito upang lumikha ng isang imahe ng RAM ng pahina ng data na babaguhin:

- Basahin ang pahina ng Flash program memory at iimbak ito sa data RAM bilang isang "imahe" ng data. Ang imahe ng RAM ay dapat basahin simula sa isang hangganan ng address ng pahina.

- Baguhin ang imahe ng data ng RAM kung kinakailangan.

Erasing Flash Program Memory

Pagkatapos makumpleto ang Hakbang 1 at 2 sa itaas, gawin ang sumusunod na apat na hakbang upang burahin ang pahina ng memorya ng programa ng Flash:

- Itakda ang NVMOP[3:0] bits (NVMCON[3:0]) para burahin ang page ng Flash program memory read mula sa Hakbang 1.

- Isulat ang panimulang address ng pahinang mabubura sa mga rehistro ng NVMADRU at NMVADR.

- Sa mga interrupt na hindi pinagana:

- a) Isulat ang key sequence sa NVMKEY register para paganahin ang pagtatakda ng WR bit (NVMCON[15]).

- b) Itakda ang WR bit; ito ay magsisimula ng erase cycle.

- c) Magsagawa ng dalawang tagubilin sa NOP.

- Ang WR bit ay na-clear kapag ang cycle ng bura ay kumpleto na.

Pagprograma ng Pahina ng Flash Memory

Ang susunod na bahagi ng proseso ay ang pag-program ng pahina ng Flash memory. Ang pahina ng Flash memory ay na-program gamit ang data mula sa imahe na ginawa sa Hakbang 1. Ang data ay inililipat sa mga write latches sa mga pagtaas ng alinman sa mga double instruction na salita o mga hilera. Ang lahat ng mga aparato ay may double instruction word programming kakayahan. (Sumangguni sa kabanata ng “Flash Program Memory” sa partikular na data sheet ng device upang matukoy kung, at anong uri ng, row programming ang available.) Pagkatapos ma-load ang mga write latches, sinisimulan ang pagpapatakbo ng programming, na naglilipat ng data mula sa magsulat ng mga latch sa Flash memory. Ito ay paulit-ulit hanggang sa ang buong pahina ay na-program. Ulitin ang sumusunod na tatlong hakbang, simula sa unang salita ng pagtuturo ng pahina ng Flash at dagdagan ang mga hakbang ng alinman sa dobleng salita ng programa, o mga hilera ng pagtuturo, hanggang sa ma-program ang buong pahina:

- I-load ang mga write latches:

- a) Itakda ang rehistro ng TBLPAG upang ituro ang lokasyon ng mga write latches.

- b) I-load ang gustong bilang ng mga trangka gamit ang mga pares ng TBLWTL at TBLWTH na mga tagubilin:

- Para sa double-word programming, dalawang pares ng TBLWTL at TBLWTH na mga tagubilin ang kinakailangan

- Para sa row programming, kinakailangan ang isang pares ng TBLWTL at TBLWTH na mga tagubilin para sa bawat elemento ng row ng salita ng pagtuturo

- Simulan ang pagpapatakbo ng programming:

- a) Itakda ang NVMOP[3:0] bits (NVMCON[3:0]) upang i-program ang alinman sa double instruction na salita o isang instruction row, kung naaangkop.

b) Isulat ang unang address ng alinman sa double instruction word o instruction row na ipoprogram sa NVMADRU at NVMADR registers.

c) Sa mga interrupt na hindi pinagana:

• Isulat ang key sequence sa NVMKEY register para paganahin ang pagtatakda ng WR bit (NVMCON[15])

• Itakda ang WR bit; ito ay magsisimula ng erase cycle

• Magsagawa ng dalawang tagubilin sa NOP

- a) Itakda ang NVMOP[3:0] bits (NVMCON[3:0]) upang i-program ang alinman sa double instruction na salita o isang instruction row, kung naaangkop.

- Ang WR bit ay na-clear kapag ang programming cycle ay kumpleto na.

Ulitin ang buong proseso kung kinakailangan upang i-program ang nais na dami ng Flash program memory.

Tandaan

- Dapat tandaan ng user na ang pinakamababang halaga ng Flash program memory na maaaring mabura gamit ang RTSP ay isang pahinang binura. Samakatuwid, mahalaga na ang isang imahe ng mga lokasyong ito ay maiimbak sa pangkalahatang layunin na RAM bago simulan ang isang ikot ng pagbura.

- Ang isang hilera o salita sa Flash program memory ay hindi dapat ma-program nang higit sa dalawang beses bago mabura.

- Sa mga device na may Configuration bytes na naka-imbak sa huling page ng Flash, ang pagsasagawa ng page bura operation sa huling page ng program memory ay na-clear ang Configuration bytes, na nagbibigay-daan sa proteksyon ng code. Sa mga device na ito, hindi dapat mabura ang huling pahina ng Flash memory.

ERASING ONE PAGE OF FLASH

Ang pagkakasunod-sunod ng code na ipinapakita sa HalampAng 4-1 ay maaaring gamitin upang burahin ang isang pahina ng Flash program memory. Ang rehistro ng NVMCON ay na-configure upang burahin ang isang pahina ng memorya ng programa. Ang mga rehistro ng NVMADR at NMVADRU ay na-load ng panimulang address ng pahina na mabubura. Ang memorya ng programa ay dapat mabura sa isang "kahit" na hangganan ng address ng pahina. Tingnan ang kabanata ng “Flash Program Memory” ng partikular na data sheet ng device upang matukoy ang laki ng Flash page.

Ang operasyon ng bura ay sinisimulan sa pamamagitan ng pagsulat ng isang espesyal na pag-unlock, o key sequence, sa NVMKEY register bago itakda ang WR bit (NVMCON[15]). Ang pagkakasunud-sunod ng pag-unlock ay kailangang isagawa sa eksaktong pagkakasunud-sunod, tulad ng ipinapakita sa Halample 4-1, nang walang pagkaantala; samakatuwid, ang mga pagkagambala ay dapat na hindi pinagana.

Dalawang tagubilin sa NOP ang dapat ipasok sa code pagkatapos ng ikot ng pagbura. Sa ilang partikular na device, ang Configuration bits ay naka-store sa huling page ng program Flash. Sa mga device na ito, ang pagsasagawa ng pagpapatakbo ng pagbubura ng pahina sa huling pahina ng memorya ng program ay binubura ang mga byte ng Flash Configuration, na nagpapagana ng proteksyon ng code bilang resulta. Ang mga gumagamit ay hindi dapat magsagawa ng mga pagpapatakbo ng pagbubura ng pahina sa huling pahina ng memorya ng programa.

LOADING WRITE LATCHES

Ang mga write latches ay ginagamit bilang isang mekanismo ng imbakan sa pagitan ng application ng user na Table Writes at ang aktwal na pagkakasunud-sunod ng programming. Sa panahon ng pagpapatakbo ng programming, ililipat ng device ang data mula sa mga write latches sa Flash memory. Para sa mga device na sumusuporta sa row programming, HalampIpinapakita ng le 4-3 ang pagkakasunud-sunod ng mga tagubilin na maaaring magamit upang mag-load ng 128 write latches (128 instruction words). 128 TBLWTL at 128 TBLWTH na mga tagubilin ay kailangan upang mai-load ang mga write latches para sa pagprograma ng isang hilera ng Flash program memory. Sumangguni sa kabanata ng “Flash Program Memory” ng partikular na data sheet ng device upang matukoy ang bilang ng mga programming latch na available sa iyong device. Para sa mga device na hindi sumusuporta sa row programming, HalampAng le 4-4 ay nagpapakita ng pagkakasunod-sunod ng mga tagubilin na maaaring magamit upang i-load ang dalawang write latches (dalawang instruction words). Dalawang TBLWTL at dalawang TBLWTH na tagubilin ang kailangan para i-load ang mga write latches.

Tandaan

- Ang code para sa Load_Write_Latch_Row ay ipinapakita sa Halample 4-3 at ang code para sa Load_Write_Latch_Word ay ipinapakita sa Halampsa 4-4. Ang code sa parehong ex na itoamples ang tinutukoy sa kasunod na examples.

- Sumangguni sa partikular na sheet ng data ng device para sa bilang ng mga latch.

SINGLE ROW PROGRAMMING EXAMPLE

Ang rehistro ng NVMCON ay naka-configure upang magprograma ng isang hilera ng Flash program memory. Ang pagpapatakbo ng programa ay sinisimulan sa pamamagitan ng pagsulat ng isang espesyal na pag-unlock, o key sequence, sa NVMKEY register bago itakda ang WR bit (NVMCON[15]). Ang pagkakasunud-sunod ng pag-unlock ay kailangang isagawa nang walang pagkaantala, at sa eksaktong pagkakasunud-sunod, tulad ng ipinapakita sa Exampsa 4-5. Samakatuwid, ang mga interrupt ay dapat na hindi pinagana bago isulat ang pagkakasunud-sunod.

Tandaan: Hindi lahat ng device ay may kakayahan sa row programming. Sumangguni sa kabanata ng “Flash Program Memory” ng partikular na data sheet ng device upang matukoy kung available ang opsyong ito.

Dalawang tagubilin sa NOP ang dapat ipasok sa code pagkatapos ng cycle ng programming.

ROW PROGRAMMING GAMIT ANG RAM BUFFER

Ang mga piling dsPIC33 device ay nagpapahintulot sa row programming na direktang gumanap mula sa isang buffer space sa data RAM, sa halip na dumaan sa mga holding latches upang maglipat ng data gamit ang mga tagubilin sa TBLWT. Ang lokasyon ng RAM buffer ay tinutukoy ng NVMSRCADR register(s), na na-load ng data RAM address na naglalaman ng unang salita ng data ng program na isusulat.

Bago isagawa ang pagpapatakbo ng programa, ang buffer space sa RAM ay dapat na mai-load ng hilera ng data na ma-program. Ang RAM ay maaaring i-load sa alinman sa isang naka-compress (naka-pack) o hindi naka-compress na format. Gumagamit ang compressed storage ng isang data word para iimbak ang Most Significant Bytes (MSBs) ng dalawang katabing program data words. Ang hindi naka-compress na format ay gumagamit ng dalawang salita ng data para sa bawat salita ng data ng programa, na ang itaas na byte ng bawat iba pang salita ay 00h. Ang naka-compress na format ay gumagamit ng humigit-kumulang 3/4 ng espasyo sa data RAM kumpara sa hindi naka-compress na format. Ang hindi naka-compress na format, sa kabilang banda, ay ginagaya ang istraktura ng 24-bit na salita ng data ng programa, na kumpleto sa itaas na phantom byte. Ang format ng data ay pinili ng RPDF bit (NVMCON[9]). Ang dalawang format na ito ay ipinapakita sa Figure 4-1.

Kapag na-load na ang RAM buffer, ang Flash Address Pointer, NVMADR at NVMADRU, ay na-load ng 24-bit na panimulang address ng Flash row na isusulat. Tulad ng pagprograma ng write latches, ang proseso ay sinisimulan sa pamamagitan ng pagsulat ng NVM unlock sequence, na sinusundan ng pagtatakda ng WR bit. Kapag nasimulan na, awtomatikong nilo-load ng device ang mga tamang latch at dinadagdagan ang mga nairehistrong NVM Address hanggang sa ma-program na ang lahat ng byte. HalampAng 4-7 ay nagpapakita ng isang example ng proseso. Kung ang NVMSRCADR ay nakatakda sa isang halaga na ang data underrun error ay nangyayari, ang URERR bit (NVMCON[8]) ay itatakda upang ipahiwatig ang kundisyon.

Ang mga device na nagpapatupad ng RAM buffer row programming ay nagpapatupad din ng isa o dalawang write latches. Ang mga ito ay na-load gamit ang mga tagubilin ng TBLWT at ginagamit upang magsagawa ng mga pagpapatakbo ng word programming.

WORD PROGRAMMING

Ang rehistro ng NVMCON ay naka-configure upang magprograma ng dalawang salita ng pagtuturo ng memorya ng programa ng Flash. Ang pagpapatakbo ng programa ay sinisimulan sa pamamagitan ng pagsulat ng isang espesyal na pag-unlock, o key sequence, sa NVMKEY register bago itakda ang WR bit (NVMCON[15]). Ang pagkakasunud-sunod ng pag-unlock ay kailangang isagawa sa eksaktong pagkakasunud-sunod, tulad ng ipinapakita sa Halample 4-8, nang walang pagkaantala. Samakatuwid, ang mga interrupt ay dapat na hindi pinagana bago isulat ang pagkakasunud-sunod.

Dalawang tagubilin sa NOP ang dapat ipasok sa code pagkatapos ng cycle ng programming.

Pagsusulat sa Mga Rehistro ng Configuration ng Device

Sa ilang partikular na device, ang Configuration bits ay iniimbak sa configuration memory space sa isang seksyong tinatawag na, “Device Configuration Registers”. Sa iba pang mga device, ang Configuration bits ay naka-store sa huling page ng program Flash user memory space sa isang seksyon na tinatawag na, "Flash Configuration Bytes". Sa mga device na ito, ang pagsasagawa ng pagpapatakbo ng pagbubura ng pahina sa huling pahina ng memorya ng program ay binubura ang mga byte ng Flash Configuration, na nagbibigay-daan sa proteksyon ng code. Samakatuwid, ang mga gumagamit ay hindi dapat magsagawa ng mga pagpapatakbo ng pagbubura ng pahina sa huling pahina ng memorya ng programa. Sumangguni sa Program Memory Map sa "Memory Organization" na kabanata ng partikular na data sheet ng device upang matukoy kung saan matatagpuan ang Configuration bits.

Kapag ang Configuration bits ay naka-store sa configuration memory space, maaaring gamitin ang RTSP para sumulat sa device Configuration registers, at pinapayagan ng RTSP ang bawat Configuration register na isa-isang muling isulat nang hindi muna nagsasagawa ng erase cycle. Dapat mag-ingat kapag isinusulat ang mga rehistro ng Configuration dahil kinokontrol ng mga ito ang mga kritikal na parameter ng pagpapatakbo ng device, gaya ng source clock system, PLL at WDT enable.

Ang pamamaraan para sa pagprograma ng rehistro ng Configuration ng device ay katulad ng pamamaraan para sa pagprograma ng Flash program memory, maliban na ang mga tagubilin ng TBLWTL lamang ang kinakailangan. Ito ay dahil ang itaas na walong bits sa bawat rehistro ng Configuration ng device ay hindi ginagamit. Higit pa rito, ang bit 23 ng Table Write address ay dapat itakda upang ma-access ang mga rehistro ng Configuration. Sumangguni sa “Device Configuration” (DS70000618) sa “dsPIC33/PIC24 Family Reference Manual” at sa “Special Features” chapter sa partikular na data sheet ng device para sa buong paglalarawan ng mga rehistro ng Configuration ng device.

Tandaan

- Ang pagsusulat sa mga rehistro ng Configuration ng device ay hindi available sa lahat ng device. Sumangguni sa kabanata ng "Mga Espesyal na Tampok" sa partikular na data sheet ng device upang matukoy ang mga mode na available ayon sa kahulugan ng NVMOP[3:0] bits na partikular sa device.

- Habang nagsasagawa ng RTSP sa mga rehistro ng Configuration ng device, dapat gumana ang device gamit ang panloob na FRC Oscillator (walang PLL). Kung gumagana ang device mula sa ibang pinagmulan ng orasan, ang switch ng orasan sa panloob na FRC Oscillator (NOSC[2:0] = 000) ay dapat gawin bago isagawa ang pagpapatakbo ng RTSP sa mga rehistro ng Configuration ng device.

- Kung ang Primary Oscillator Mode Select bits (POSCMD[1:0]) sa Oscillator Configuration register (FOSC) ay na-reprogram sa isang bagong value, dapat tiyakin ng user na ang Clock Switching Mode bits (FCKSM[1:0]) ay nasa ang rehistro ng FOSC ay may paunang naka-program na halaga na '0', bago isagawa ang operasyong ito ng RTSP.

CONFIGURATION REGISTER WRITE ALGORITHM

Ang pangkalahatang pamamaraan ay ang mga sumusunod:

- Isulat ang bagong halaga ng pagsasaayos sa Table Write latch gamit ang isang pagtuturo ng TBLWTL.

- I-configure ang NVMCON para sa isang Configuration register write (NVMCON = 0x4000).

- Isulat ang address ng Configuration register na ipo-program sa NVMADRU at NVMADR registers.

- Huwag paganahin ang mga pagkagambala, kung pinagana.

- Isulat ang key sequence sa NVMKEY register.

- Simulan ang write sequence sa pamamagitan ng pagtatakda ng WR bit (NVMCON[15]).

- Muling paganahin ang mga pagkagambala, kung kinakailangan.

ExampAng 4-10 ay nagpapakita ng pagkakasunud-sunod ng code na maaaring magamit upang baguhin ang isang rehistro ng Configuration ng device.

REGISTER MAPA

Ang isang buod ng mga rehistro na nauugnay sa Flash Programming ay ibinigay sa Talahanayan 5-1.

Inililista ng seksyong ito ang mga tala ng aplikasyon na nauugnay sa seksyong ito ng manwal. Ang mga tala ng aplikasyon na ito ay maaaring hindi partikular na isinulat para sa mga pamilya ng produkto ng dsPIC33/PIC24, ngunit ang mga konsepto ay may kinalaman at maaaring gamitin nang may pagbabago at posibleng mga limitasyon. Ang kasalukuyang mga tala ng aplikasyon na nauugnay sa Flash Programming ay:

Tandaan: Mangyaring bisitahin ang Microchip weblugar (www.microchip.com) para sa karagdagang Application Notes at code examples para sa mga dsPIC33/PIC24 na pamilya ng mga device.

KASAYSAYAN NG REBISYON

Rebisyon A (Agosto 2009)

Ito ang unang inilabas na bersyon ng dokumentong ito.

Rebisyon B (Pebrero 2011)

Kasama sa rebisyong ito ang mga sumusunod na update:

- Examples:

- Inalis Halample 5-3 at Halampsa 5-4

- Na-update Halample 4-1, Halample 4-5 at Halampsa 4-10

- Ang anumang mga reference sa #WR ay na-update sa #15 sa Halample 4-1, Halample 4-5 at Halampsa 4-8

- Na-update ang sumusunod sa Halampika-4-3:

- Na-update ang pamagat na "Word Programming" sa "Naglo-load ng Write Latches para sa Row Programming"

- Ang anumang reference sa #ram_image ay na-update sa #0xFA

- Idinagdag Halampsa 4-4

- Na-update ang pamagat sa Halampsa 4-8

- Mga Tala:

- Nagdagdag ng dalawang tala sa Seksyon 4.2 “Flash Programming Operations”

- Na-update ang tala sa Seksyon 4.5.2 “Naglo-load ng mga Write Latches”

- Nagdagdag ng tatlong tala sa Seksyon 4.6 "Pagsusulat sa Mga Rehistro ng Configuration ng Device"

- Idinagdag ang Tala 1 sa Talahanayan 5-1

- Mga Register:

- Na-update ang mga bit value para sa NVMOP[3:0]: NVM Operation Pumili ng mga bit sa rehistro ng Flash Memory Control (NVMCON) (tingnan ang Register 3-1)

- Mga Seksyon:

- Inalis ang mga seksyon 5.2.1.4 "Write Word Mode" at 5.2.1.5 "Write Byte Mode"

- Na-update na Seksyon 3.0 "Mga Rehistro ng Kontrol"

- Na-update ang sumusunod sa Seksyon 4.5.5 “Word Programming”:

- Pinalitan ang pamagat ng seksyon na "Pagprograma ng Isang Salita ng Flash Memory" sa "Pagprograma ng Salita"

- Na-update ang unang talata

- Pinalitan ang mga terminong "isang salita" sa "isang pares ng mga salita" sa ikalawang talata

- Nagdagdag ng bagong Hakbang 1 sa Seksyon 4.6.1 “Configuration Register Write Algorithm”

- Mga talahanayan:

- Na-update ang Talahanayan 5-1

- Ang ilang mga sanggunian sa memorya ng programa ay na-update sa memorya ng programa ng Flash

- Ang iba pang mga menor de edad na pag-update tulad ng mga update sa wika at pag-format ay isinama sa buong dokumento

Rebisyon C (Hunyo 2011)

Kasama sa rebisyong ito ang mga sumusunod na update:

- Examples:

- Na-update Halampsa 4-1

- Na-update Halampsa 4-8

- Mga Tala:

- Nagdagdag ng tala sa Seksyon 4.1 “RTSP Operation”

- Idinagdag ang Tala 3 sa Seksyon 4.2 “Flash Programming Operations”

- Idinagdag ang Tala 3 sa Seksyon 4.2.1 “RTSP Programming Algorithm”

- Added a note in Section 4.5.1 “Erasing One Page of Flash”

- Idinagdag ang Tala 2 sa Seksyon 4.5.2 "Naglo-load ng mga Write Latches"

- Mga Register:

- Na-update ang paglalarawan ng bit para sa mga bit 15-0 sa rehistro ng Nonvolatile Memory Address (tingnan ang Register 3-3)

- Mga Seksyon:

- Na-update na Seksyon 4.1 “RTSP Operation”

- Na-update na Seksyon 4.5.5 “Word Programming”

- Ang iba pang mga menor de edad na pag-update tulad ng mga update sa wika at pag-format ay isinama sa buong dokumento

Rebisyon D (Disyembre 2011)

Kasama sa rebisyong ito ang mga sumusunod na update:

- Na-update na Seksyon 2.1.3 “Table Write Latches”

- Na-update ang Seksyon 3.2 “NVMKEY Register”

- Na-update ang mga tala sa NVMCON: Flash Memory Control Register (tingnan ang Register 3-1)

- Ang mga malawak na pag-update ay ginawa sa buong Seksyon 4.0 "Run-Time Self-Programming (RTSP)"

- Ang iba pang mga menor de edad na pag-update tulad ng mga update sa wika at pag-format ay isinama sa buong dokumento

Rebisyon E (Oktubre 2018)

Kasama sa rebisyong ito ang mga sumusunod na update:

- Idinagdag Halample 2-2, Halample 4-2, Halample 4-6 at Halampsa 4-9

- Idinagdag ang Seksyon 4.5.4 "Row Programming Gamit ang RAM Buffer"

- Na-update na Seksyon 1.0 “Introduction”, Seksyon 3.3 “NVM Address Registers”, Seksyon 4.0 “Run-Time Self-Programming (RTSP)” at Seksyon 4.5.3 “Single Row Programming Example ”

- Nai-update na Register 3-1

- Na-update Halampsa 4-7

- Na-update ang Talahanayan 5-1

Rebisyon F (Nobyembre 2021)

Idinagdag ang Seksyon 3.2.1 "Pag-disable ng mga Interrupt".

Na-update Halample 3-1, Halample 4-1, Halample 4-2, Halample 4-5, Halample 4-6, Halample 4-7, Halample 4-8, Halample 4-9 at Halampsa 4-10.

Updated Section 3.2 “NVMKEY Register”, Section 4.5.1 “Erasing One Page of Flash”, Section 4.5.3 “Single Row Programming Example” at Seksyon 4.6.1 “Configuration Register Write Algorithm”.

Tandaan ang mga sumusunod na detalye ng tampok na proteksyon ng code sa mga produkto ng Microchip:

- Ang mga produktong Microchip ay nakakatugon sa mga pagtutukoy na nakapaloob sa kanilang partikular na Microchip Data Sheet.

- Naniniwala ang Microchip na ang pamilya ng mga produkto nito ay ligtas kapag ginamit sa inilaan na paraan, sa loob ng mga pagtutukoy sa pagpapatakbo, at sa ilalim ng normal na mga kondisyon.

- Pinahahalagahan ng Microchip at agresibong pinoprotektahan ang mga karapatan sa intelektwal na pag-aari nito. Mahigpit na ipinagbabawal ang mga pagtatangkang labagin ang mga tampok na proteksyon ng code ng produkto ng Microchip at maaaring lumabag sa Digital Millennium Copyright Act.

- Ni ang Microchip o anumang iba pang tagagawa ng semiconductor ay hindi magagarantiyahan ang seguridad ng code nito. Ang proteksyon ng code ay hindi nangangahulugan na ginagarantiya namin na ang produkto ay "hindi nababasag". Ang proteksyon ng code ay patuloy na umuunlad. Ang Microchip ay nakatuon sa patuloy na pagpapabuti ng mga tampok sa proteksyon ng code ng aming mga produkto

Ang publikasyong ito at ang impormasyon dito ay maaari lamang gamitin sa mga produkto ng Microchip, kabilang ang pagdidisenyo, pagsubok, at pagsasama ng mga produktong Microchip sa iyong aplikasyon. Ang paggamit ng impormasyong ito sa anumang iba pang paraan ay lumalabag sa mga tuntuning ito. Ang impormasyon tungkol sa mga application ng device ay ibinibigay lamang para sa iyong kaginhawahan at maaaring mapalitan ng mga update. Responsibilidad mong tiyakin na ang iyong aplikasyon ay nakakatugon sa iyong mga detalye. Makipag-ugnayan sa iyong lokal na opisina ng pagbebenta ng Microchip para sa karagdagang suporta o, kumuha ng karagdagang suporta sa https://www.microchip.com/en-us/support/design-help/client-supportservices.

ANG IMPORMASYON NA ITO AY IBINIGAY NG MICROCHIP "AS IS". ANG MICROCHIP ay WALANG GUMAWA NG MGA REPRESENTASYON O WARRANTY NG ANUMANG URI MAHALAGA MAN O IPINAHIWATIG, NAKASULAT O BALIG, STATUTORY O IBA PA, NA KAUGNAY SA IMPORMASYON KASAMA NGUNIT HINDI LIMITADO SA ANUMANG IPINAHIWATIG NA WARRANTI NG HINDI PAGSASANIB, AT PAGKAKATAO, MGA WARRANTY NA KAUGNAY SA KUNDISYON, KALIDAD, O PAGGANAP NITO. HINDI MANANAGOT ANG MICROCHIP SA ANUMANG INDIRECT, ESPESYAL, PUNITIVE, INCIDENTAL, O KAHITANG PAGKAWALA, PINSALA, GASTOS, O GASTOS NG ANUMANG URI NA KAUGNAY SA IMPORMASYON O SA PAGGAMIT NITO, GAANO MAN ANG SANHI, KAHIT NA MINSAN ANG MAGING POSIBILIDAD O ANG MGA PINSALA AY MAAABOT. HANGGANG SA KABUUSAN NA PINAHAYAGAN NG BATAS, ANG KABUUANG PANANAGUTAN NG MICROCHIP SA LAHAT NG MGA CLAIMS SA ANUMANG PARAAN NA KAUGNAY SA IMPORMASYON O PAGGAMIT NITO AY HINDI HIGIT SA HALAGA NG MGA BAYAD, KUNG MERON, NA DIREKTA NINYONG BINAYARAN SA MICROCHIP PARA SA IMPORMASYON.

Ang paggamit ng mga aparatong Microchip sa suporta sa buhay at/o mga aplikasyong pangkaligtasan ay ganap na nasa panganib ng mamimili, at sumasang-ayon ang bumibili na ipagtanggol, bayaran at hawakan ang Microchip na hindi nakakapinsala sa anuman at lahat ng pinsala, paghahabol, paghahabla, o gastos na nagreresulta mula sa naturang paggamit. Walang mga lisensya ang ipinadala, nang tahasan o kung hindi man, sa ilalim ng anumang mga karapatan sa intelektwal na ari-arian ng Microchip maliban kung iba ang nakasaad.

Para sa impormasyon tungkol sa Quality Management System ng Microchip, pakibisita www.microchip.com/quality.

Mga trademark

Ang pangalan at logo ng Microchip, logo ng Microchip, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash , Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, at XMEGA ay mga rehistradong trademark ng Microchip Technology Incorporated sa USA at iba pang mga bansa. AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet- Wire, Ang SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, WinPath, at ZL ay mga rehistradong trademark ng Microchip Technology Incorporated sa USA

Katabing Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DEM Average Matching , ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified na logo, MPLIB, MPLINK, MultiTRAK, NetDetach, NVM Express, NVMe, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE , Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-IS, storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewAng Span, WiperLock, XpressConnect, at ZENA ay mga trademark ng Microchip Technology Incorporated sa USA at iba pang mga bansa.

Ang SQTP ay isang marka ng serbisyo ng Microchip Technology Incorporated sa USA

Ang logo ng Adaptec, Frequency on Demand, Silicon Storage Technology, Symmcom, at Trusted Time ay mga rehistradong trademark ng Microchip Technology Inc. sa ibang mga bansa.

Ang GestIC ay isang rehistradong trademark ng Microchip Technology Germany II GmbH & Co. KG, isang subsidiary ng Microchip Technology Inc., sa ibang mga bansa.

Ang lahat ng iba pang trademark na binanggit dito ay pag-aari ng kani-kanilang kumpanya.

© 2009-2021, Microchip Technology Incorporated at mga subsidiary nito.

Lahat ng Karapatan ay Nakalaan.

ISBN: 978-1-5224-9314-3

Pandaigdigang Benta at Serbisyo

AMERIKA

- Tanggapan ng Kumpanya

2355 West Chandler Blvd.

Chandler, AZ 85224-6199

Tel: 480-792-7200

Fax: 480-792-7277

Teknikal na Suporta: http://www.microchip.com/

suporta Web Address: www.microchip.com - Atlanta

Duluth, GA

Tel: 678-957-9614

Fax: 678-957-1455 - Austin, TX

Tel: 512-257-3370 - Boston

Westborough, MA

Tel: 774-760-0087

Fax: 774-760-0088 - Chicago

Itasca, IL

Tel: 630-285-0071

Fax: 630-285-0075 - Dallas

Addison, TX

Tel: 972-818-7423

Fax: 972-818-2924 - Detroit

Novi, MI

Tel: 248-848-4000 - Houston, TX

Tel: 281-894-5983 - Indianapolis

Noblesville, IN

Tel: 317-773-8323

Fax: 317-773-5453

Tel: 317-536-2380 - Los Angeles

Mission Viejo, CA

Tel: 949-462-9523

Fax: 949-462-9608

Tel: 951-273-7800 - Raleigh, NC

Tel: 919-844-7510 - New York, NY

Tel: 631-435-6000 - San Jose, CA

Tel: 408-735-9110

Tel: 408-436-4270 - Canada - Toronto

Tel: 905-695-1980

Fax: 905-695-2078

ASIA/PACIFIC

- Australia – Sydney

Tel: 61-2-9868-6733 - Tsina - Beijing

Tel: 86-10-8569-7000 - Tsina – Chengdu

Tel: 86-28-8665-5511 - Tsina – Chongqing

Tel: 86-23-8980-9588 - Tsina – Dongguan

Tel: 86-769-8702-9880 - Tsina - Guangzhou

Tel: 86-20-8755-8029 - Tsina - Hangzhou

Tel: 86-571-8792-8115 - China – Hong Kong SAR

Tel: 852-2943-5100 - Tsina – Nanjing

Tel: 86-25-8473-2460 - Tsina – Qingdao

Tel: 86-532-8502-7355 - Tsina - Shanghai

Tel: 86-21-3326-8000 - Tsina – Shenyang

Tel: 86-24-2334-2829 - Tsina - Shenzhen

Tel: 86-755-8864-2200 - Tsina - Suzhou

Tel: 86-186-6233-1526 - Tsina - Wuhan

Tel: 86-27-5980-5300 - Tsina – Xian

Tel: 86-29-8833-7252 - Tsina – Xiamen

Tel: 86-592-2388138 - Tsina – Zhuhai

Tel: 86-756-3210040 - India – Bangalore

Tel: 91-80-3090-4444 - India – New Delhi

Tel: 91-11-4160-8631 - India - Pune

Tel: 91-20-4121-0141 - Japan – Osaka

Tel: 81-6-6152-7160 - Japan – Tokyo

Tel: 81-3-6880- 3770 - Korea – Daegu

Tel: 82-53-744-4301 - Korea – Seoul

Tel: 82-2-554-7200 - Malaysia - Kuala Lumpur

Tel: 60-3-7651-7906 - Malaysia – Penang

Tel: 60-4-227-8870 - Pilipinas – Maynila

Tel: 63-2-634-9065 - Singapore

Tel: 65-6334-8870 - Taiwan – Hsin Chu

Tel: 886-3-577-8366 - Taiwan – Kaohsiung

Tel: 886-7-213-7830 - Taiwan - Taipei

Tel: 886-2-2508-8600 - Thailand – Bangkok

Tel: 66-2-694-1351 - Vietnam – Ho Chi Minh

Tel: 84-28-5448-2100

EUROPE

- Austria – Wels

Tel: 43-7242-2244-39

Fax: 43-7242-2244-393 - Denmark – Copenhagen

Tel: 45-4485-5910

Fax: 45-4485-2829 - Finland – Espoo

Tel: 358-9-4520-820 - France - Paris

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79 - Alemanya – Garching

Tel: 49-8931-9700 - Alemanya – Haan

Tel: 49-2129-3766400 - Alemanya - Heilbronn

Tel: 49-7131-72400 - Alemanya - Karlsruhe

Tel: 49-721-625370 - Alemanya - Munich

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44 - Alemanya - Rosenheim

Tel: 49-8031-354-560 - Italya - Milan

Tel: 39-0331-742611

Fax: 39-0331-466781 - Italya - Padova

Tel: 39-049-7625286 - Netherlands – Drunen

Tel: 31-416-690399

Fax: 31-416-690340 - Norway - Trondheim

Tel: 47-7288-4388 - Poland - Warsaw

Tel: 48-22-3325737 - Romania – Bucharest

Tel: 40-21-407-87-50 - Espanya - Madrid

Tel: 34-91-708-08-90

Fax: 34-91-708-08-91 - Sweden - Gothenberg

Tel: 46-31-704-60-40 - Sweden - Stockholm

Tel: 46-8-5090-4654 - UK – Wokingham

Tel: 44-118-921-5800

Fax: 44-118-921-5820

Tandaan:

Ang seksyong ito ng family reference manual ay nilalayong magsilbi bilang pandagdag sa mga sheet ng data ng device. Depende sa variant ng device, maaaring hindi nalalapat ang manual na seksyong ito sa lahat ng dsPIC33/PIC24 device. Mangyaring kumonsulta sa tala sa simula ng "Flash Program Memory" na kabanata sa kasalukuyang sheet ng data ng device upang tingnan kung sinusuportahan ng dokumentong ito ang device na iyong ginagamit.

Ang mga sheet ng data ng device at mga seksyon ng manual reference ng pamilya ay magagamit para sa pag-download mula sa Microchip Worldwide Website sa: http://www.microchip.com.

Mga Dokumento / Mga Mapagkukunan

|

MICROCHIP PIC24 Flash Programming [pdf] Gabay sa Gumagamit PIC24 Flash Programming, PIC24, Flash Programming, Programming |

|

MICROCHIP PIC24 Flash Programming [pdf] Gabay sa Gumagamit PIC24 Flash Programming, PIC24, Flash Programming |